## EVOLVABLE HARDWARE DESIGN OF COMBINATIONAL LOGIC CIRCUITS

By

Tatiana G. Kalganova

SUBMITTED IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY AT NAPIER UNIVERSITY EDINBURGH, SCOTLAND MAY 2000

© Copyright by Tatiana G. Kalganova, 2000

#### DECLARATION OF ORIGINALITY

I hereby declare that this thesis and the work contained herein was composed and originated entirely by myself, other than those items acknowledged in the text. The work was completed under a full-time supervised program at Napier University between September 1997 and May 2000.

Some materials presented in the thesis has been published as follows: Chapter 3 in [1]; Chapter 4 in [1], [2], [3]; Chapter 5 in [4], [5]; Chapter 6 in [6]; Chapter 7 in [7], [8], [9].

Some peripheral but related work, not described in this thesis, has been published in [2].

Dated: May 2000

Tatiana G. Kalganova

## To my family.

iii

.

### Abstract

Evolvable Hardware (EHW), as an alternative method for logic design, became more attractive recently, because of its algebra-independent techniques for generating selfadaptive self-reconfigurable hardware. This thesis investigates and relates both evaluation and evolutionary processes, emphasizing the need to address problems arising from data complexity.

Evaluation processes, capable of evolving cost-optimised fully functional circuits are investigated. The need for an extrinsic EHW approach (software models) independent of the concerns of any implementation technologies is emphasized. It is also shown how the function description may be adapted for use in the EHW approach. A number of issues of evaluation process are addressed: these include choice of optimisation criteria, multi-objective optimisation techniques in EHW and probabilistic analysis of evolutionary processes.

The concept of self-adaptive extrinsic EHW method is developed. This approach emphasizes the circuit layout evolution together with circuit functionality. A chromosome representation for such system is introduced, and a number of genetic operators and evolutionary algorithms in support of this approach are presented. The genetic operators change the genetic material at the different levels of chromosome representation. Furthermore, a chromosome representation is adapted to the function-level EHW approach. As a result, the modularised systems are evolved using multi-output building blocks. This chromosome representation overcomes the problem of long string chromosome.

Together, these techniques facilitate the construction of systems to evolve logic functions of large number of variables. A method for achieving this using bidirectional incremental evolution is documented. It is demonstrated that the integration of a dynamic evaluation process and self-adaptive function-level EHW approach allows the bidirectional incremental evolution to successfully evolve more complex systems than traditionally evolved before. Thereby it provides a firm foundation for the evolution of complex systems.

Finally, the universality of these techniques is proved by applying them to multivalued combinational logic design. Empirical study of this application shows that there is no fundamental difference in approach for both binary and multi-valued logic design problems.

### Acknowledgments

First and foremost I wish to express my thanks to and acknowledge the assistance of all those people without whom this thesis would not exist.

Firstly thanks are due to my two supervisors, Prof. T.C. Fogarty (South Bank University) and Prof. A. Almaini (Napier University) who supervised the work reported here.

Thanks are due to the School of Computing at Napier University and EvoNet office for providing support for this work under my PhD student grant. I would also like to give special thanks to Dr. J. Miller who originated the approach that I extended and investigated.

I would also like to thank the following who helped me in various ways during my life as a PhD student: L. Miramontes Hercog (South Bank University), N. Gonet (University of Edinburgh), S.-H. Choi (Napier University), J. Bautista Ortega (Rosslin Institute, University of Edinburgh), A. Stoica (NASA), J. Willies (EvoNet), Marjory and Geoff Horne, Christine and Paul Deponio. Thanks also to my parents for support, Galina Kalganova (my mother) and Gennady Kalganov (my father) for emotional support during the writing of this dissertation, and my nephews, Sasha and Pasha Lipnitskie, for providing such a wonderful distraction during my visit to Belarus. Special thanks to my sister, Natalia Lipnitskaya for our long chats and discussion, for emotional support that I was getting from her during time of writing this work. Finally and especially I would like to thank Olivier Fouquet for his encouragement and understanding.

## **Table of Contents**

| Τa            | able o                    | f Contents ix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|---------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Li            | List of Tables x          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| $\mathbf{Li}$ | st of                     | Figures xvi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| $\mathbf{Li}$ | st of                     | Symbols xxix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

| 1             | Intr<br>1.1<br>1.2<br>1.3 | Deduction       1         Objectives       1         The outline of the dissertation       2         Some remarks about terminology used in the dissertation       6                                                                                                                                                                                                                                                                                                                                            |  |  |

| 2             | Evo<br>2.1<br>2.2<br>2.3  | utionary design of electronic circuits8Circuit design problem and evolutionary algorithms8Main concept of Evolvable Hardware11Taxonomy of Evolvable Hardware122.3.1Evaluation process132.3.2Evolutionary process182.3.3Evolutionary programming approach212.3.4Target application area232.3.5Evolving platform29An extrinsic EHW in digital circuit design362.4.1Louis's EHW approach362.4.2Cartesian GP382.4.3Assemble and Test412.4.4Advantages of an extrinsic EHW432.4.5Disadvantages of an extrinsic EHW44 |  |  |

|               | 2.5                       | 2.4.5Disadvantages of an extrinsic EHW44Incremental Evolution45                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |

|   | 2.6  | Motivation of presented research                                                              | 50  |

|---|------|-----------------------------------------------------------------------------------------------|-----|

|   | 2.7  | Scope of this Dissertation                                                                    | 52  |

|   | 2.8  | Contribution to knowledge                                                                     | 54  |

|   | 2.9  | Summary                                                                                       | 54  |

| 3 | Ana  | alysis and verification of evolved circuits                                                   | 56  |

|   | 3.1  | Introduction                                                                                  | 56  |

|   | 3.2  | An extrinsic gate-level EHW                                                                   | 58  |

|   | 3.3  | Function representation in an extrinsic EHW                                                   | 58  |

|   |      | 3.3.1 Boolean functions specified by truth and minterms tables                                | 59  |

|   |      | 3.3.2 Boolean functions specified by cubes                                                    | 62  |

|   | 3.4  | Fitness function strategies                                                                   | 69  |

|   |      | 3.4.1 Pareto Optimum                                                                          | 70  |

|   |      | 3.4.2 Criteria used in an extrinsic EHW                                                       | 71  |

|   |      | 3.4.3 Dynamic fitness function, $\mathcal{F}_1 + \mathcal{F}_2 \dots \dots \dots \dots \dots$ | 74  |

|   |      | 3.4.4 Method of objective weighting                                                           | 77  |

|   |      | 3.4.5 Method of distance functions                                                            | 78  |

|   |      | 3.4.6 MIN-MAX formulation                                                                     | 79  |

|   |      | 3.4.7 Experimental results                                                                    | 80  |

|   | 3.5  | Evolutionary processes specified by dynamic fitness function and their                        |     |

|   |      |                                                                                               | 100 |

|   |      |                                                                                               | 100 |

|   |      |                                                                                               | 108 |

|   | 3.6  | Summary                                                                                       | 118 |

| 4 | Circ | cuit layout evolution                                                                         | 122 |

|   | 4.1  |                                                                                               | 122 |

|   | 4.2  |                                                                                               | 124 |

|   | 4.3  |                                                                                               | 133 |

|   |      | 4.3.1 Encoding                                                                                | 133 |

|   |      | 4.3.2 Objective Function and Fitness                                                          | 137 |

|   | 4.4  | Evolutionary Algorithm                                                                        | 138 |

|   |      | 4.4.1 Initialisation                                                                          | 138 |

|   |      | 4.4.2 Mutation                                                                                | 139 |

|   |      | 4.4.3 Recombination                                                                           | 143 |

|   | 4.5  | Experimental results                                                                          | 145 |

|   |      | 4.5.1 Crossover and mutation strategies                                                       | 145 |

|   |      | 4.5.2 Dynamic fitness strategy in heterogeneous circuit layout evolution                      | 155 |

|   |      | 4.5.3 Distributions of circuit layout and circuit functionality                               | 158 |

|          | 4.6 | Summary                                                                    | 164 |

|----------|-----|----------------------------------------------------------------------------|-----|

| <b>5</b> | Fun | ction level extrinsic EHW                                                  | 168 |

|          | 5.1 | Introduction                                                               | 168 |

|          | 5.2 | Chromosome representation                                                  | 169 |

|          |     | 5.2.1 Encoding                                                             | 169 |

|          |     | 5.2.2 Fitness Function                                                     | 177 |

|          | 5.3 | Connection repair algorithm                                                | 180 |

|          | 5.4 | Experimental results                                                       | 182 |

|          |     | 5.4.1 Algorithm performance                                                | 183 |

|          |     | 5.4.2 Evolved circuits                                                     | 186 |

|          | 5.5 | Summary                                                                    | 198 |

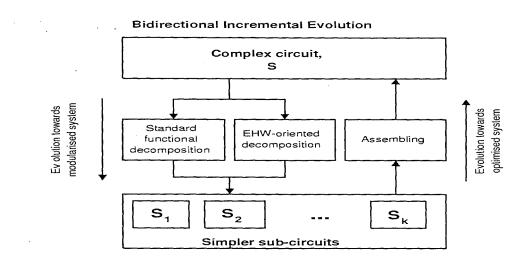

| 6        | Bid | irectional incremental evolution                                           | 200 |

|          | 6.1 | Introduction                                                               | 201 |

|          | 6.2 | Basic idea of bidirectional incremental evolution applied to digital logic |     |

|          |     | design                                                                     | 206 |

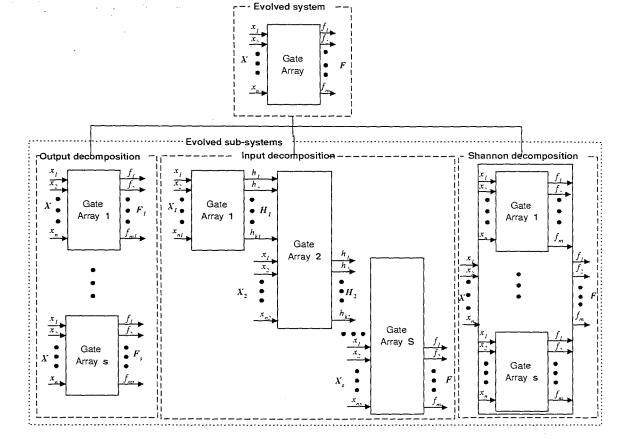

|          | 6.3 | BIE with standard functional decomposition                                 | 209 |

|          |     | 6.3.1 Statement of problem                                                 | 209 |

|          |     | 6.3.2 Standard functional decomposition methods                            | 212 |

|          |     | 6.3.3 Experiment A: BIE with Shannon's decomposition                       | 215 |

|          |     | 6.3.4 Experiment B: BIE with output decomposition                          | 222 |

|          | 6.4 | BIE with EHW-oriented decomposition                                        | 226 |

|          |     | 6.4.1 Stage 1. Evolution towards a modularised system using EHW-           |     |

|          |     | oriented decomposition                                                     | 227 |

|          |     | 6.4.2 Stage 2. Evolution towards an optimised system                       | 232 |

|          |     | 6.4.3 Experiment C: BIE with output decomposition                          | 232 |

|          |     | 6.4.4 Experiment D: BIE with Shannon's and output decompositions           | 239 |

|          | 6.5 | Summary                                                                    | 252 |

| 7        | Mu  | lti-valued logic circuit design                                            | 254 |

|          | 7.1 | Introduction                                                               | 255 |

|          | 7.2 | Idea of EHW approach                                                       | 257 |

|          | 7.3 | Background and notations                                                   | 258 |

|          | 7.4 | An extrinsic EHW                                                           | 262 |

|          |     | 7.4.1 Encoding                                                             | 262 |

|          |     | 7.4.2 Fitness Function                                                     | 271 |

|          | 7.5 | Evolved circuit designs for arithmetic circuits                            | 273 |

|          |     | 7.5.1 A half adder, add3_2.pla                                             | 273 |

|              |       | 7.5.2 An one-digit full adder, add3_3c.pla                              | 275 |

|--------------|-------|-------------------------------------------------------------------------|-----|

|              |       | 7.5.3 An one-digit multiplier, mult3_2.pla                              | 277 |

|              |       | 7.5.4 A 1.5-digit multiplier, mult3_3.pla                               | 278 |

|              | 7.6   | Gate-level EHW and algorithm performance                                | 280 |

|              |       | 7.6.1 Circuit layout and algorithm performance                          | 280 |

|              |       | 7.6.2 Influence the functional set of logic gates used on the algorithm |     |

|              |       | performance                                                             | 289 |

|              | 7.7   | Comparison of function and gate level EHW                               | 292 |

|              | 7.8   | Summary                                                                 | 293 |

| 8            | Con   | aclusions                                                               | 296 |

|              | 8.1   | Future work                                                             | 300 |

| A            | Apr   | pendix. Digital circuit design                                          | 302 |

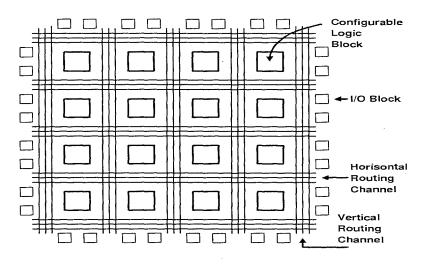

|              |       | Implementation technologies                                             | 302 |

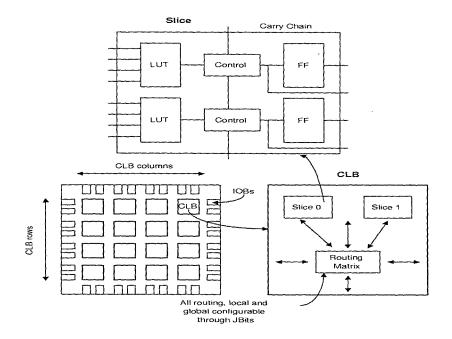

|              |       | A.1.1 FPGA                                                              | 302 |

|              |       | A.1.2 Xilinx FPGA                                                       | 303 |

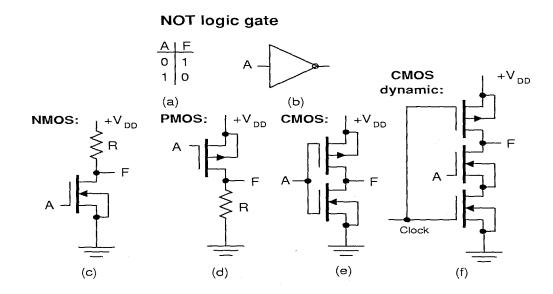

|              |       | A.1.3 Unipolar logic families                                           | 305 |

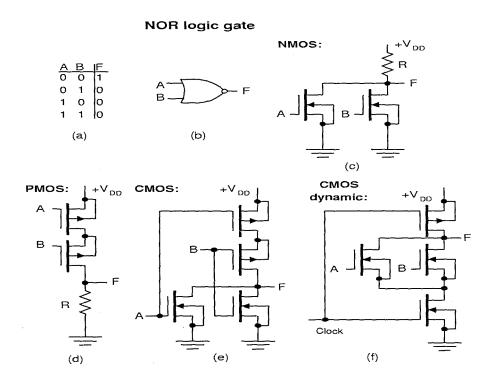

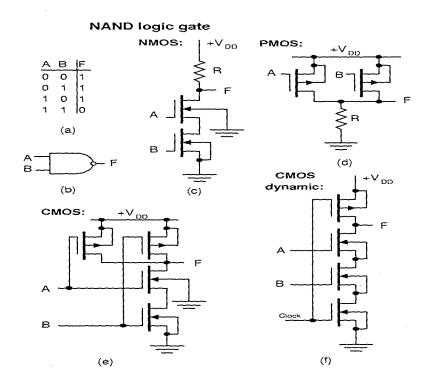

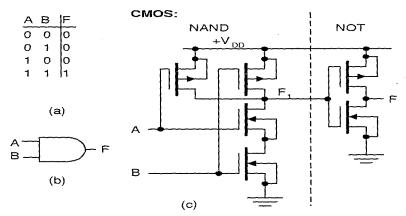

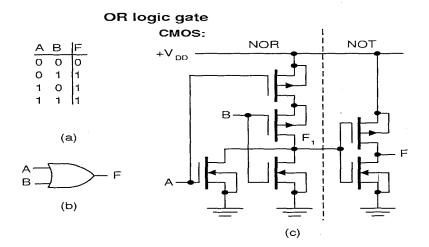

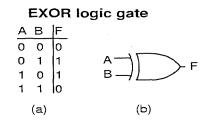

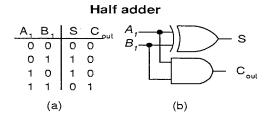

|              | A.2   | Primitive logic gates and their implementation                          | 307 |

|              |       | A.2.1 Comparison of logic gate implementations                          | 311 |

|              | A.3   | Combinational building blocks                                           | 311 |

| в            | Apŗ   | pendix. The functional set of logic gates and EHW performance           | 315 |

| С            | App   | pendix. Evolved optimal two-bit multiplier designs                      | 322 |

| D            | Cor   | nputational effort of EHW approach                                      | 325 |

| $\mathbf{E}$ | App   | pendix. Distinctive features of the TPRODUCT operator                   | 327 |

| F            | App   | pendix. Distinctive features of the TSUM operator                       | 334 |

| Bi           | bliog | graphy                                                                  | 336 |

ix

### List of Tables

2.1Summary of extrinsic EHW approaches for digital circuit design VGA is a variable-length chromosome GA; GP and EP are a Genetic and an Evolutionary Programming; CGP is a Cartesian GP; AS is an Ant System; f(n,m,r) is an *n*-input *m*-output *r*-valued logic function;  $f_{mux}(3,1,2)$  is a logic function describing the behaviour of multiplexer;  $\mathcal{F}$  is a fitness function;  $F_1$  defines a correctness of outputs of network evolved;  $F_2$  is the minimal number of logic cells used;  $F_3$  is a correctness of input combinations;  $F_4$  is an error based fitness,  $\mathcal{F}_1 + \mathcal{F}_2$  is a dynamic fitness function strategy with execution of criteria  $F_1$  at first stage of evolutionary process and criteria  $\overline{F_2}$  at the second stage; p is the number of input combinations in the logic 342.2Cell gate functionality. 40 Development of cartesian GP. IE is an incremental evolution; ES is an 2.3evolutionary strategy; GA is a genetic algorithm; VES and VGA are the variable-length chromosome ES and GA respectively; f(n, m, r) is an ninput *m*-output *r*-valued logic function;  $f_{mux}(3,1,2)$  is an logic function described the behaviour of multiplexer;  $F_1$  defines the correctness of outputs of logic circuit evolved;  $F_2$  is the minimal number of logic cells used;  $F_3$  is the correctness of input combinations;  $F_4$  is an error based fitness;  $\mathcal{F}_1 + \mathcal{F}_2$ 42is a dynamic fitness function. 3.1A 5-digit even parity function given by minterms table (xor5\_d.pla)

and by truth table (xor5\_d1.pla).  $X = \{x_0, x_1, x_2, x_3, x_4\}, Y = \{y_0\}$ .

60

| 3.2 | The ternary operations.                                                                                                           | 63  |

|-----|-----------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.3 | Boolean logic function given by truth table.                                                                                      | 64  |

| 3.4 | A tested function given by the cube representation (ternary_test2.pla)                                                            |     |

|     | and by the truth table (binary_test2.pla). $X = \{x_0, x_1, x_2, x_3\}, Y =$                                                      |     |

|     | $\{y_0, y_1, y_2\}$                                                                                                               | 65  |

| 3.5 | Initial data: Evolving logic functions using gate-level extrinsic EHW.                                                            |     |

|     | $N_{in}^{max}(\mathcal{B})$ is the maximum number of inputs in the building block $\mathcal{B}$ . $\mathcal{F}_1 + \mathcal{F}_2$ |     |

|     | is the dynamic fitness function. The truth table representation of logic func-                                                    |     |

|     | tion corresponds to applying binary logic in EHW and the cube representa-                                                         |     |

|     | tion - to ternary logic. $\ldots$                | 67  |

| 3.6 | Experimental results: Fitness function strategy and algorithm perfor-                                                             |     |

|     | mance. X denotes that the corresponding criteria has been activated; $\overline{F_1^{bf}}$ ,                                      |     |

|     | $\overline{F_2^{bf}}$ and $\overline{F_3^{bf}}$ are the mean fitnesses $F_1$ , $F_2$ and $F_3$ of the best evolved                |     |

|     | chromosomes respectively; $\overline{F_2(\mathcal{N}_f)}$ is the mean fitness function $F_2$ of fully                             |     |

|     | functional designs evolved during 100 runs; $\mathcal{R}(\mathcal{N}_f)$ is the number of evolved                                 |     |

|     | fully functional circuits, $\mathcal{N}_f$                                                                                        | 83  |

| 3.7 | Initial data: Evolving logic functions optimised by different criteria.                                                           |     |

|     | Functional set $\mathbb{FS}_j$ is encoded according to the Table 2.2                                                              | 89  |

| 3.8 | Experimental results: Dynamic fitness function strategy using different                                                           |     |

|     | optimisation parameters at the second stage of evolution. $\mathcal{F}_1$ and $\mathcal{F}_2$ are                                 |     |

|     | the first and second criteria of the dynamic fitness function $\mathcal{F}$ , $(\mathcal{F}_1 = F_1)$ ;                           |     |

|     | $F_{4CMOS}$ , $F_{4DMOS}$ and $F_{4NMOS}$ are the number of transistors in CMOS,                                                  |     |

|     | dynamic MOS and NMOS circuits respectively; $\overline{F_k^{bf}}$ is the mean value of                                            |     |

|     | criteria $F_k$ for the best evolved chromosomes; $N_f$ is the fully functional                                                    |     |

|     | circuit; $\overline{F_2(\mathcal{N}_f)}$ is the mean fitness function $F_2$ of $N_f$ evolved during 100                           |     |

|     | runs; $\mathcal{R}(\mathcal{N}_f)$ is the number of evolved fully functional circuits, $\mathcal{N}_f$                            | 90  |

| 3.9 | An example of generating a differential chromosome. $\mathbb{C}_1$ and $\mathbb{C}_2$ are two                                     |     |

|     | compared chromosomes; $\mathbb D$ is the differential chromosome; $\mathbf o = \{o_1 \ o_2\}$ is the                              |     |

|     | circuit output vector; $\mathcal{F}_{\mathbb{C}_i}$ and $\mathcal{F}_{\mathbb{D}}$ are the fitness functions of chromosomes       |     |

|     | $\mathbb{C}_i 	ext{ and } \mathbb{D}$ respectively                                                                                | 103 |

| 3.10 | Initial data Probabilistic analysis. $N_{in}^{max}(\mathcal{B})$ is the maximum number of                           |     |

|------|---------------------------------------------------------------------------------------------------------------------|-----|

|      | inputs in the building block $\mathcal{B}$                                                                          | 110 |

| 3.11 | The functional characteristics of chosen functional sets                                                            | 111 |

| 3.12 | Experimental Results: $\overline{F_1^{bf}}$ and $\overline{F_2^{bf}}$ are the mean fitnesses $F_1$ and $F_2$ of the |     |

|      | best evolved chromosomes respectively; $\overline{F_2(\mathcal{N}_f)}$ denotes the average fitness                  |     |

|      | $F_2$ for fully functional circuits evolved; $N_f$ is the fully functional circuit;                                 |     |

|      | $R(\mathcal{N}_f)$ defines the number of fully functional circuits evolved                                          | 116 |

| 4.1  | Initial data: Circuit layout and algorithm performance. The EA pa-                                                  |     |

|      | rameters used in this experiment and further in experimental results have                                           |     |

|      | been chosen according to empirical study of EA behaviour. $\ldots$ .                                                | 126 |

| 4.2  | Gate functionality according to the $b_0(z)$ gene in chromosome $\ldots$ .                                          | 136 |

| 4.3  | Initial data: Circuit layout evolution using elite genetic algorithm.                                               |     |

|      | $\mathcal{F}_1 + \mathcal{F}_2$ is the dynamic fitness with estimation of the number of active gates                |     |

|      | in circuit; GGM, BGM and LGM are the global, boundary, local geometry                                               |     |

|      | mutations.                                                                                                          | 147 |

| 4.4  | Experimental results: Using circuit mutation and geometry mutation.                                                 | 148 |

| 4.5  | Experimental results: Using geometry mutation only, heterogeneous                                                   |     |

|      | geometry.                                                                                                           | 149 |

| 4.6  | Experimental results: Using circuit mutation only, homogeneous ge-                                                  |     |

|      | ometry 4x4(add1c.pla) and 5x5(mult2.pla)                                                                            | 150 |

| 4.7  | Experimental results: Using circuit mutation only, heterogeneous ge-                                                |     |

|      | ometry at the initialisation stage.                                                                                 | 152 |

| 4.8  | Experimental results: Using circuit and geometry mutation, heteroge-                                                |     |

|      | neous geometry.                                                                                                     | 153 |

| 4.9  | Initial data: Dynamic fitness function and heterogeneous circuit geom-                                              |     |

|      | etry; $\mathcal{F}_1 + \mathcal{F}_2$ is the dynamic fitness with estimation of the number of                       |     |

|      | active gates in circuit; GGM, BGM and LGM are the global, boundary,                                                 |     |

|      | local geometry mutations.                                                                                           | 156 |

|      |                                                                                                                     |     |

| 4.10 | Experimental results: Strategies of fitness function; $F_1$ and $\mathcal{F}_1 + \mathcal{F}_2$ are |     |

|------|-----------------------------------------------------------------------------------------------------|-----|

|      | the fitness without and with estimation of the number of active gates                               |     |

|      | in circuit respectively; GM is the geometry mutation.                                               | 157 |

| 4.11 | Initial data: Circuit layout distribution                                                           | 160 |

| 4.12 | Experimental results: Algorithm performance during investigation of                                 |     |

|      | the circuit layout and circuit functionality distributions                                          | 160 |

| 4.13 | Experimental results: The circuit functionality distribution. Results                               |     |

|      | show that the higher number of circuits has been evolved with higher circuit                        |     |

|      | functionality.                                                                                      | 163 |

| 5.1  | Gate functionality according to the $b_0(z)$ gene in chromosome $\ldots$ .                          | 170 |

| 5.2  | Initial data                                                                                        | 184 |

| 5.3  | Experimental Results. Functional sets shown in bold correspond to the                               |     |

|      | function-level EHW approach, otherwise - to gate-level EHW                                          | 185 |

| 6.1  | Initial data: Evolving the sub-functions of sqn_d.pla synthesized using                             |     |

|      | Shannon's decomposition and function-level extrinsic EHW.                                           | 215 |

| 6.2  | sqn_d.pla: Specification of sub-circuits evolved by BIE with standard                               |     |

|      | decomposition. OD and SD are the output and the Shannon's decomposi-                                |     |

|      | tions (by inputs) respectively; FEHW is the function-level EHW; $n, m$ and $p$                      |     |

|      | are the number of inputs, outputs and input combinations in the subsystem                           |     |

|      | evolved; $k$ is the number of additional logic gates involved to connect sub-                       |     |

|      | systems; $F_2(N_f^{opt})$ is the number of active logic gates in the most efficient                 |     |

|      | evolved circuit.                                                                                    | 217 |

| 6.3  | z5xp1_d.pla: Metrics of sub-systems obtained during evolution. The                                  |     |

|      | systems are decomposed according to the metrics shown in bold. For exam-                            |     |

|      | ple, after analysis of the system $S_2$ , the easily evolved system $S_3$ is composed               |     |

|      | from the outputs $y_0$ , $y_5$ and $y_6$ . The remaining outputs are evaluated in the               |     |

|      | following system $S_4$                                                                              | 235 |

| 6.4  | z5xp1_d.pla: History of the incremental evolution with the EHW-                                     |     |

|      | oriented output decomposition.                                                                      | 241 |

| 6.5 | Parameters of $S_0$ sub-system obtained during evolution of $z 5xp1_d$ .pla.                              |     |

|-----|-----------------------------------------------------------------------------------------------------------|-----|

|     | The metrics specified in Eq. 6.4.1 and Eq. 6.4.2 are calculated for sub-                                  |     |

|     | system $S_0$ . $f_{y_j}^o$ defines that the sub-function described by output $y_j$ is                     |     |

|     | fully functional. Metrics $f_{y_j}^{io} _{x_i=0}$ and $f_{y_j}^{io} _{x_i=1}$ correspond to the Shannon's |     |

|     | decomposition by variable $x_i$ . Hence, $f_{y_j}^{io} _{x_i=0} = f_{y_j}^{io} _{x_i=1} = 100$ for all    |     |

|     | variables $x_i$ . If $f_{y_i}^o < 100$ and $f_{y_j}^{io} _{x_i=0} = 100$ then the sub-circuit described   |     |

|     | the sub-function with $x_i = 0$ is fully functions. The same implied for metric                           |     |

|     | $f_{y_j}^{io} _{x_i=1}$                                                                                   | 242 |

| 6.6 | Parameters of sub-systems obtained during evolution of z5xp1_d.pla                                        |     |

|     | using the EHW-oriented output and input decompositions (Stage 1.                                          |     |

|     | Evolution towards a modularised system).                                                                  | 243 |

| 6.7 | z5xp1_d.pla: History of the bidirectional incremental evolution with                                      |     |

|     | the EHW-oriented output and input decomposition                                                           | 249 |

| 7.1 | Gate functionality according to the $b_0(z)$ gene in chromosome $\ldots$ .                                | 263 |

| 7.2 | Truth tables for the circuits shown in Fig. 7.5 (c), (d) and (b) $\ .$                                    | 275 |

| 7.3 | Initial data: Circuit layout and algorithm performance                                                    | 282 |

| 7.4 | Initial data: Functional set of logic gates and algorithm performance.                                    | 290 |

| 7.5 | Experimental Results: Functional set of logic gates and algorithm                                         |     |

|     | performance. Experimental data shows that the algorithm performance                                       |     |

|     | strongly depends on the functional set of logic gates chosen. Similar con-                                |     |

|     | clusion has been made for binary combinational logic design problem (see                                  |     |

|     | Appendix B)                                                                                               | 291 |

| 7.6 | Initial data: Performance of gate and function level extrinsic evolvable                                  |     |

|     | hardware approaches                                                                                       | 294 |

$\operatorname{xiv}$

7.7 Experimental Results: Performance of the gate and the function level extrinsic evolvable hardware. Experimental data obtained show that the function-level EHW approach performs better than the gate-level EHW. This confirms the universality of the EHW approach in question, since similar results have been obtained when the binary combinational logic design problem has been considered (see Chapter 5).  $\overline{F_1^{bf}}$  and  $\overline{F_2^{bf}}$  are the mean fitnesses  $F_1$  and  $F_2$  of the best evolved chromosomes respectively;  $\overline{F_2(\mathcal{N}_f)}$  is the mean fitness function  $F_2$  of fully functional designs evolved during 100 runs;  $\mathbb{R}(\mathcal{N}_f)$  is the number of evolved fully functional circuits,  $\mathcal{N}_f \dots$  294

####

- D.1 Computational effort of EHW approach during one run to evolve the two-bit multiplier. GGM, BGM and LGM are the global, boundary and local geometry mutations respectively.

326

## List of Figures

| 2. | 1  | Circuit design problem in EHW. In Evolvable Hardware approach, the           |    |

|----|----|------------------------------------------------------------------------------|----|

|    |    | circuits in initial population are generated randomly and, therefore, do not |    |

|    |    | implement correctly the desired logic function. In EHW, an evolutionary      |    |

|    |    | algorithm designs a circuit that correctly implements a given logic function |    |

|    |    | and optimises to obtain a fully functional circuit. In other words, evolu-   |    |

|    |    | tionary algorithms evolves a logic circuit.                                  | 10 |

| 2. | 2  | EHW in electronics                                                           | 12 |

| 2. | 3  | Taxonomy of evolvable hardware.                                              | 13 |

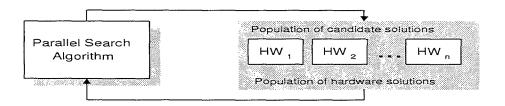

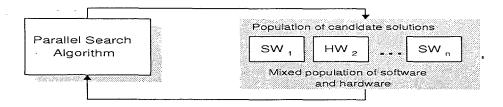

| 2. | 4  | Extrinsic EHW: evaluations of software solutions.                            | 14 |

| 2. | 5  | Intrinsic EHW: evaluations of hardware solutions                             | 14 |

| 2. | 6  | Mixtrinsic EHW: evaluations of mixed populations comprised of both           |    |

|    |    | hardware and software solutions.                                             | 16 |

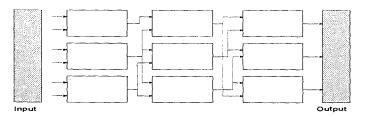

| 2. | 7  | Matrix used to represent a circuit to be processed. Each gate gets its       |    |

|    |    | inputs from either of the gates in the previous column                       | 36 |

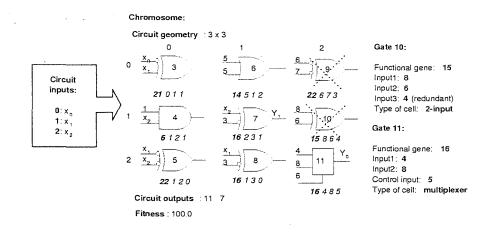

| 2. | 8  | Encoding used for each of the matrix elements that represent a circuit.      | 37 |

| 2. | 9  | An example of the phenotype and corresponding genotype of a chro-            |    |

|    |    | mosome with 3x3 circuit layout used in cartesian GP                          | 39 |

| 2. | 10 | How assemble-and-test reaches the unknown regions of the space of all        |    |

|    |    | representations.                                                             | 43 |

| 3. | 1  | A 5-digit parity circuit evolved using (a) minterms table; (b) truth         |    |

|    |    | table. Functional set: $\mathbb{FS} : \{2, 7, 8, 9\}$                        | 60 |

|    |    |                                                                              |    |

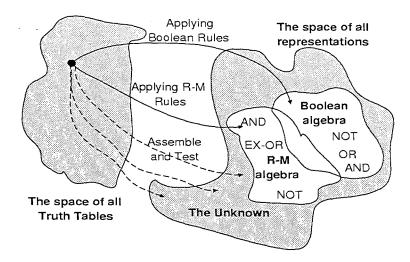

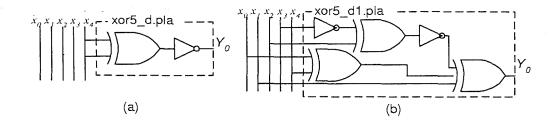

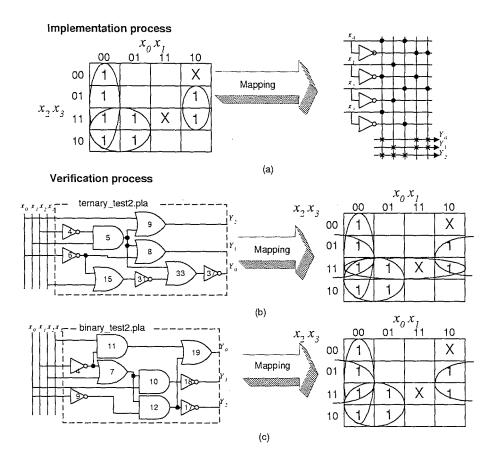

- 3.2 Implementation of logic function given in Eq. 3.3.2 (a) AND-OR PLA; In the standard logic design, the logic function is implemented according to the optimised representation, for example Karnaugh map. In given case, the PLA mapping is generated based on Karnaugh map. (b) circuit is evolved using cube representation; (c) circuit is evolved using the truth table. Unlike in the standard logic design, in EHW the circuit is synthesised independently from the representation form. In this process the representation form can be used in verification of the circuit correctness. In given case the Karnaught map is used to verify the correctness of evolved circuits.

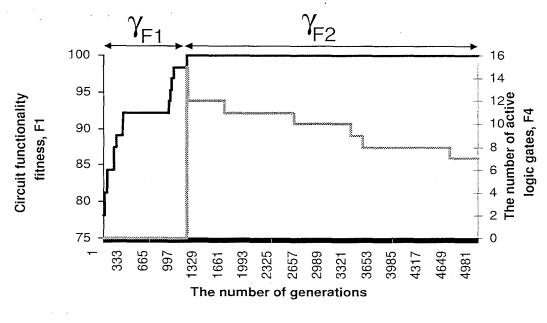

- 3.3 Behaviour of dynamic fitness function. The graph depicts the best fitnesses  $\mathcal{F}_1$  and  $\mathcal{F}_2$  of the best chromosome. The two-bit multiplier is evolved during 5000 generations using dynamic fitness function. During  $\Upsilon_{\mathcal{F}_1}$  only the circuit functionality criteria  $F_1$  is taken into account, hence  $F_4 = 0$ . During  $\Upsilon_{\mathcal{F}_2}$  the circuit functionality should remains the same  $(F_1 = 100)$ and the number of active gates is targeted to minimise. The graph shows clearly that two distinctive evolutionary processes are performed to evolve a cost-optimised fully functional two-bit multiplier. . . . . . . . . . . . .

66

76

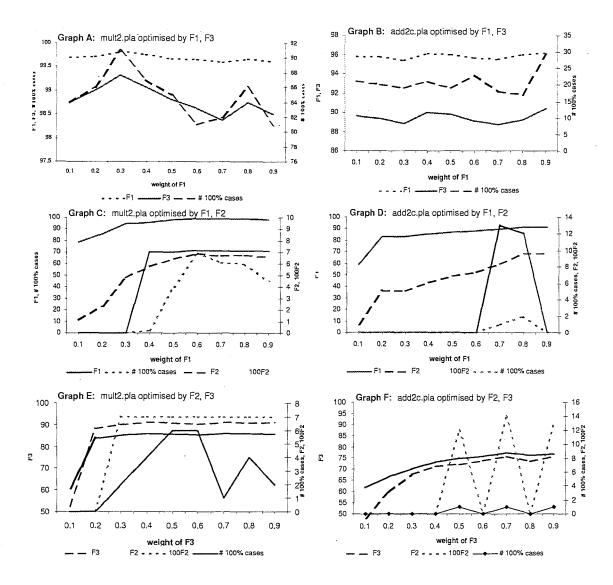

| 3.4  | Experimental results: Method of objective weighting. $F_1$ and $F_3$ define                                                                         |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | the correctness of evolved circuits; $F_2$ determines the quality of evolved                                                                        |    |

|      | circuits; Graphs A and B illustrate that there is no dominated criteria                                                                             |    |

|      | among $F_1$ and $F_3$ , since the evolutionary algorithm with different weights                                                                     |    |

|      | for both criteria performs similar for both logic functions: two-bit adder and                                                                      |    |

|      | two-bit multiplier. Graphs C and D demonstrate that $F_1$ is a dominated                                                                            |    |

|      | criterion. Thus, in the case when the weight of $F_1$ is less than the weight of                                                                    |    |

|      | $F_2$ , no fully functional solutions have been evolved for both logic functions.                                                                   |    |

|      | <b>Graphs E and F</b> evidence that $F_3$ is a dominated criterion. Similarly to                                                                    |    |

|      | the previous case, the fully functional solutions have been obtained, if the                                                                        |    |

|      | weight of $F_3$ is large enough. With increasing the weight of $F_3$ , the algorithm                                                                |    |

|      | performance has been improved. Conclusion: In evolution process is the                                                                              |    |

|      | criterion defining the correctness of evolved circuits dominates other criteria,                                                                    |    |

|      | determined the quality of evolved circuits.                                                                                                         | 84 |

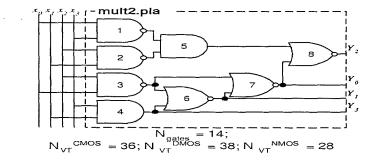

| 3.5  | Most efficient evolved two-bit multiplier design optimised by the num-                                                                              |    |

|      | ber of used transistors (A): Functional set: $\mathbb{FS}_1$ :{2, 6, 7, 8, 9, 10, 11,                                                               |    |

|      | $21, 22, 23, 24$ }                                                                                                                                  | 91 |

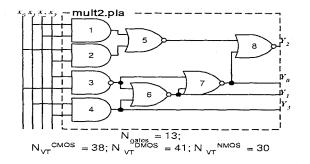

| 3.6  | Evolved two-bit multiplier design (B): Functional set: $\mathbb{FS}_2$ : {6, 10, 11,                                                                |    |

|      | $21, 22, 23, 24$ }                                                                                                                                  | 93 |

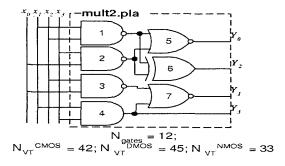

| 3.7  | Most efficient evolved two-bit multiplier design optimised by the circuit                                                                           |    |

|      | delay(C): Functional set: $\mathbb{FS}_1$ : {2, 6, 7, 8, 9, 10, 11, 21, 22, 23, 24}.                                                                | 94 |

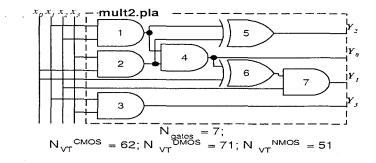

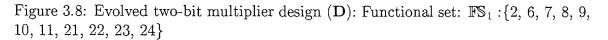

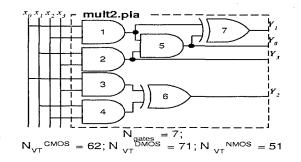

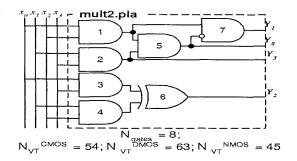

| 3.8  | Evolved two-bit multiplier design ( <b>D</b> ): Functional set: $\mathbb{FS}_1$ : {2, 6, 7, 8,                                                      |    |

|      | 9, 10, 11, 21, 22, 23, 24 $\}$                                                                                                                      | 95 |

| 3.9  | Evolved two-bit multiplier design (E): Functional set: $\mathbb{FS}_2$ : {6, 10, 11,                                                                |    |

|      | $21, 22, 23, 24$ }                                                                                                                                  | 95 |

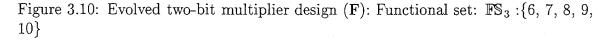

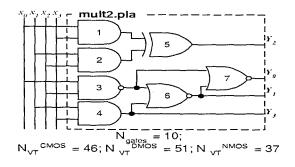

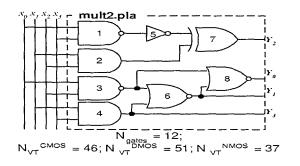

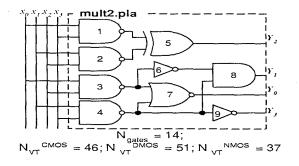

| 3.10 | Evolved two-bit multiplier design (F): Functional set: $\mathbb{FS}_3$ : {6, 7, 8, 9,                                                               |    |

|      | 10}                                                                                                                                                 | 97 |

| 3.11 | Evolved two-bit multiplier design (G): Functional set: $\mathbb{FS}_6$ : {4, 6, 10,                                                                 |    |

|      | $12, 23, 24\} \ldots \ldots$ | 98 |

xviii

- 3.12 Evolved two-bit multiplier design (I): Functional set:  $\mathbb{FS}_6$ : {4, 6, 10, 12, 23, 24} ... 98

- 3.13 Evolved two-bit multiplier design (**J**): Functional set:  $\mathbb{FS}_6$  :{4, 6, 10, 12, 23, 24} ... 99

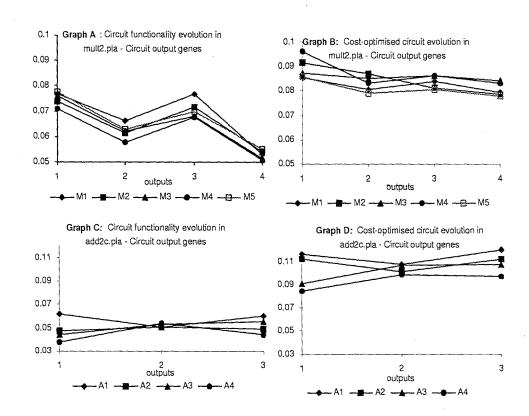

- 3.14 Circuit Output Genes. The horizontal axis defines the outputs in the evolved circuits. The vertical axes in Graphs A and C correspond to the conditional probabilities calculated according to Eq. 3.5.6 for the two-bit multiplier and the two-bit adder respectively. These graphs describe the evolutionary process aimed to evolve a fully functional circuit,  $\Upsilon_{\mathcal{F}_1}$ . Conditional probabilities calculated for both tested functions using Eq. 3.5.10 are mapped to the vertical axes of Graphs B and D. These graphs illustrate the evolutionary process that produces cost-optimised circuit,  $\Upsilon_{\mathcal{F}_2}$ . A comparison of these graphs shows that the conditional probabilities obtained for evolutionary process aimed to evolve fully functional circuits  $\Upsilon_{\mathcal{F}_1}$  2 times lower than the similar probabilities obtained for evolutionary process  $\Upsilon_{\mathcal{F}_2}$ . Conclusion: The circuit output genes are more essential during evolution  $\Upsilon_{\mathcal{F}_2}$ .

112

xix

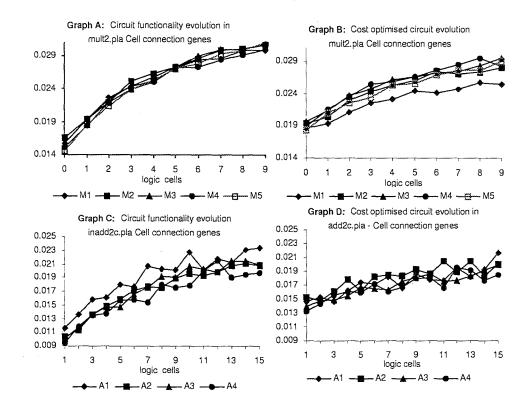

- 3.15 Connection Genes. The horizontal axis defines the positions of logic gates in the circuit layout. The vertical axes in Graphs A and C correspond to the conditional probabilities calculated according to Eq. 3.5.6 for the two-bit multiplier and the two-bit adder respectively. These graphs describe the evolutionary process aimed to evolve a fully functional circuit,  $\Upsilon_{\mathcal{F}_1}$ . Conditional probabilities calculated for both tested functions using Eq. 3.5.10 are mapped to the vertical axes of Graphs B and D. These graphs illustrate the evolutionary process that produces cost-optimised circuit,  $\Upsilon_{\mathcal{F}_2}$ . Comparison of these graphs shows that the conditional probabilities in all evolution processes are higher for genes located in more essential positions. The conditional probabilities for evolutionary process  $\Upsilon_{\mathcal{F}_2}$  in logic gates located in less essential positions are higher than the similar probabilities for evolutionary process  $\Upsilon_{\mathcal{F}_1}$ . **Conclusion:** The genes located in more essential positions are very important in both evolutionary processes. The genes located in less essential positions become more essential in evolutionary process  $\Upsilon_{\mathcal{F}_2}$ .

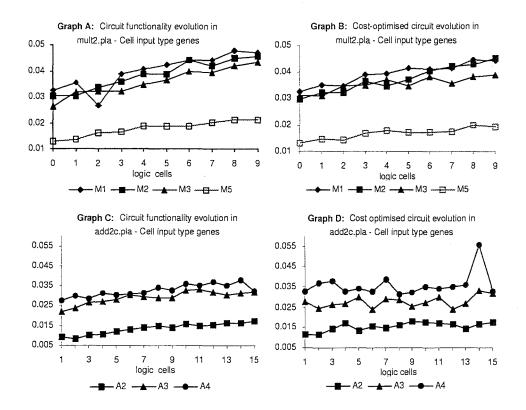

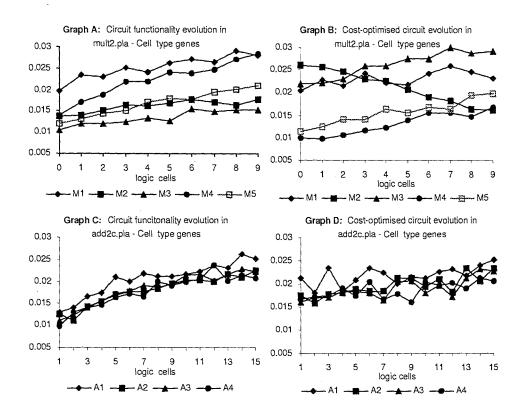

- 3.17 Cell Type Genes. The horizontal axe defines the positions of logic gates in the circuit layout. The vertical axes in Graphs A and C correspond to the conditional probabilities calculated according to Eq. 3.5.3 for the two-bit multiplier and the two-bit adder respectively. These graphs describe the evolutionary process aimed to evolve a fully functional circuit,  $\Upsilon_{\mathcal{F}_1}$ . Conditional probabilities calculated for both tested functions using Eq. 3.5.8 are mapped to the vertical axes of Graphs B and D. These graphs illustrate the evolutionary process that produces cost-optimised circuit,  $\Upsilon_{\mathcal{F}_2}$ . Comparison of these graphs shows that the conditional probabilities in all evolution processes are slightly higher for genes located in more essential positions. No differences between two evolutionary processes have been noticed for the two-bit multiplier. In case of evolving the two-bit adder, during circuit functionality evolution  $(\Upsilon_{\mathcal{F}_1})$  the conditional probabilities obtained for logic gates located in less essential positions are slightly higher than in costoptimised circuit evolution  $\Upsilon_{\mathcal{F}_2}$ . Conclusion: There is no clear difference between the two evolutionary processes for both logic functions tested. . .

115

xxi

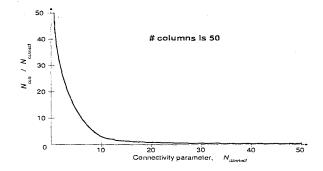

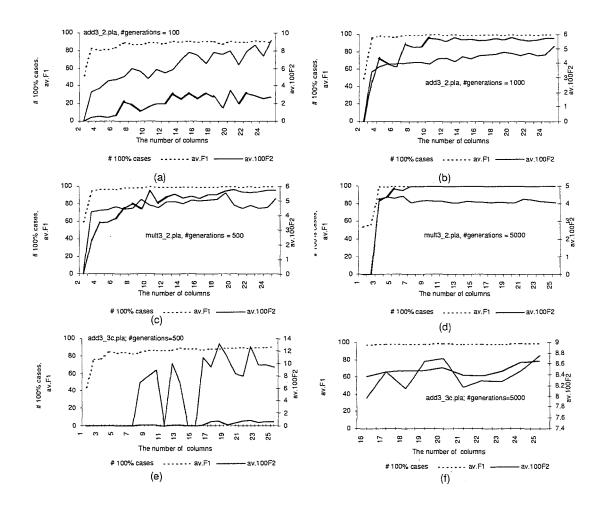

| 4.3 | Dependence of the algorithm performance on the number of columns.                      |     |

|-----|----------------------------------------------------------------------------------------|-----|

|     | Graphs A and B demonstrate that with increasing the number of columns                  |     |

|     | in the circuit without connectivity restrictions $(N_{connect} = N_{cols})$ , the num- |     |

|     | ber of primitive active logic gates in the fully functional circuits increases.        |     |

|     | Graphs C, E and G shows that with higher connectivity restrictions the                 |     |

|     | number of columns required to evolve fully functional two-bit multipliers              |     |

|     | decreases. The smaller the connectivity parameter, the narrower the range              |     |

|     | of the number of columns, that can produce fully functional solution. Simi-            |     |

|     | lar conclusion can be made considering Graphs D, F and I that correspond               |     |

|     | to the full adder                                                                      | 130 |

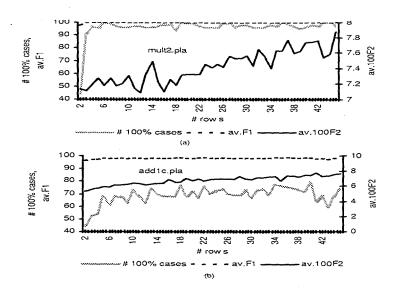

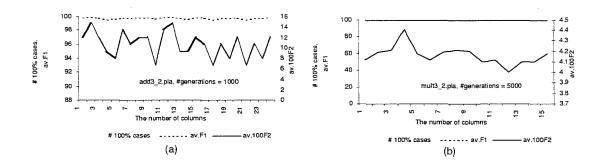

| 4.4 | Dependence the algorithm performance on the number of rows. Graphs                     | ÷   |

|     | illustrate that the algorithm performance does not depend on the number                |     |

|     | of rows in the rectangular array                                                       | 132 |

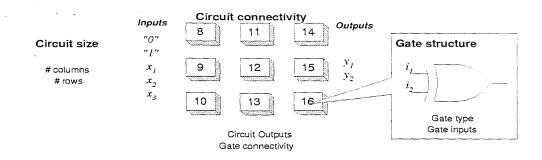

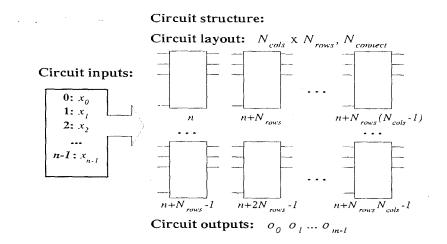

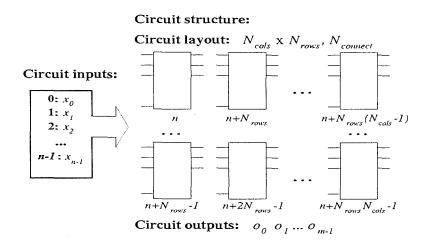

| 4.5 | Schematic of chromosome structure implementing a 3-input 2-output                      |     |

|     | logic function                                                                         | 133 |

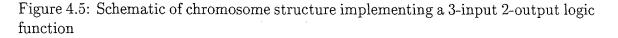

| 4.6 | An example of the phenotype and corresponding genotype of a chro-                      |     |

|     | mosome with 3x3 circuit layout                                                         | 135 |

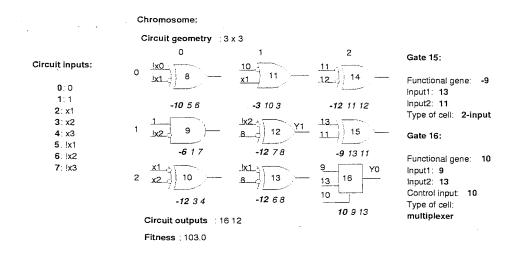

| 4.7 | The geometry mutation process for a chromosome with geometry $3x3$                     | 142 |

| 4.8 | Parents for cell-uniform crossover                                                     | 144 |

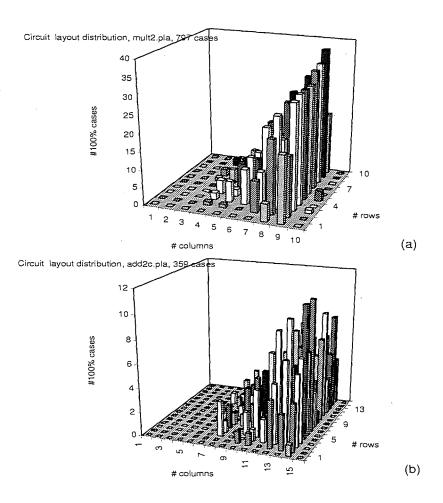

| 4.9 | The circuit layout distribution The graphs illustrate how the evolution-               |     |

|     | ary algorithm defines the circuit layout automatically and evolves the fully           |     |

| *   | functional solutions. Graphs illustrate that there is a favourite area of cir-         |     |

|     | cuit layout, where the evolutionary algorithm produces some fully functional           |     |

|     | solutions. For example, no circuit layout with 3 columns has been chosen               |     |

|     | during evolution of two-bit multiplier. In the case of the two-bit adder, no           |     |

|     | circuit layout with less than 6 columns has been chosen by evolutionary                |     |

|     | algorithm.                                                                             | 162 |

|     |                                                                                        |     |

xxii

.

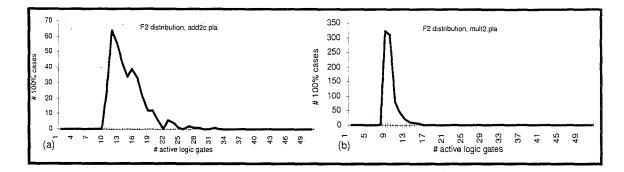

| 4.10 | The distribution of the number of active logic gates used in circuits           |     |

|------|---------------------------------------------------------------------------------|-----|

|      | evolved using circuit layout heterogeneous approach. The graphs show            |     |

|      | that there is a specific range of the number of primitive active logic          |     |

|      | gates, that contain evolved circuits.                                           | 165 |

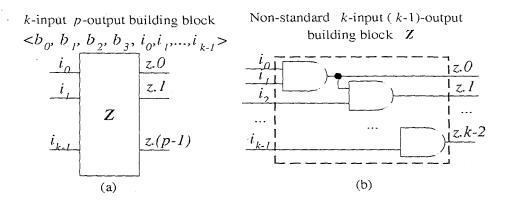

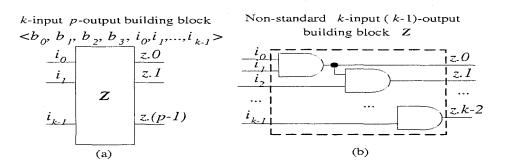

| 5.1  | Building block level representation                                             | 172 |

| 5.2  | Circuit level representation                                                    | 174 |

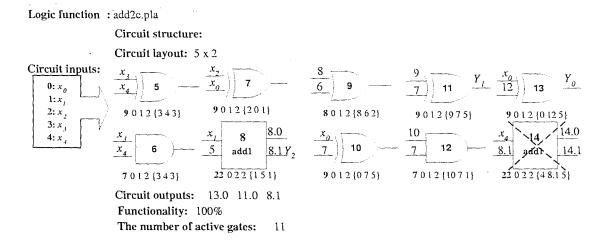

| 5.3  | An example of the phenotype and corresponding genotype of a chro-               |     |

|      | mosome with $5x2$ circuit layout The number of building blocks employed         |     |

|      | is 9. The logic gate labeled 8 implements a 1-digit full adder, that requires 3 |     |

|      | primitive logic gates to be implemented. Therefore, the number of primitive     |     |

| . •  | logic gates is 11                                                               | 176 |

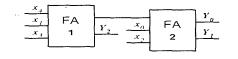

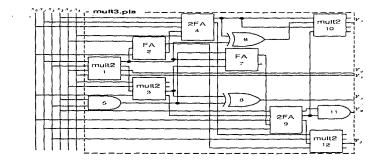

| 5.4  | Evolved two-bit adder design (A); $\#$ logic gates = 10; $\#$ building          |     |

|      | blocks = 2; HA is half adder. $\ldots$                                          | 186 |

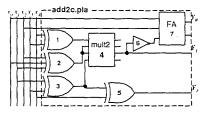

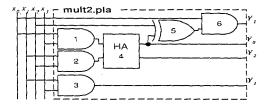

| 5.5  | Evolved two-bit adder design (B); $\#$ logic gates = 18; $\#$ building          |     |

|      | blocks = 7; FA is full adder; mult2 is a two-bit multiplier                     | 187 |

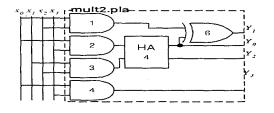

| 5.6  | Evolved two-bit multiplier design (A); $\#$ logic gates = 7; $\#$ non-          |     |

|      | redundant primitive logic gates = 7; $\#$ building blocks = 6; HA is            |     |

|      | the half adder                                                                  | 188 |

| 5.7  | Evolved two-bit multiplier design (B); $\#$ logic gates = 7; $\#$ non-          |     |

|      | redundant primitive logic gates = 7; $\#$ building blocks = 6; HA is            |     |

|      | the half adder                                                                  | 189 |

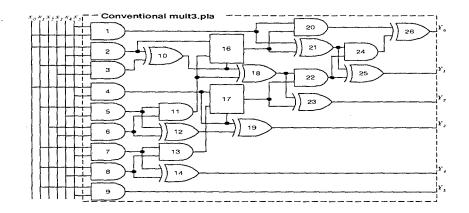

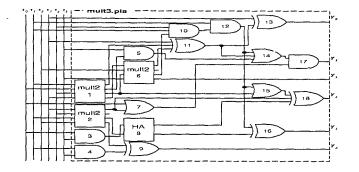

| 5.8  | Most efficient conventional gate-level three-bit multiplier (# logic gates      |     |

|      | = 34; # non-redundant primitive logic gates = 34; # building blocks             |     |

|      | = 21).                                                                          | 190 |

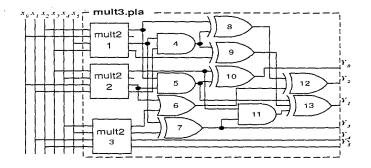

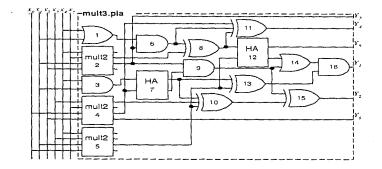

| 5.9  | Evolved 3-bit multiplier design $(A)$ : Functional set: $\{2, 7, 8, 9, 18\}$ ;  |     |

|      | # logic gates = 32; # non-redundant primitive logic gates = 28; #               |     |

|      | building blocks = 13; $mult2$ is the 2-bit multiplier                           | 191 |

xxiii

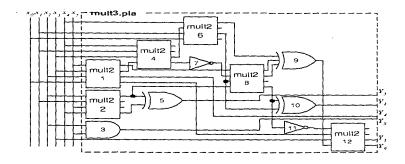

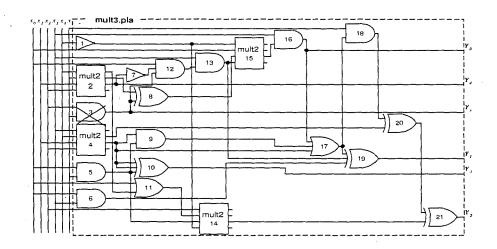

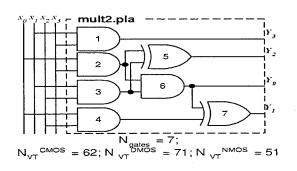

- 5.12 Evolved 3-bit multiplier (D): Functional set {2, 7, 8, 9, 18, 22};

# logic gates = 40; # non-redundant primitive logic gates = 31; #

building blocks = 16; HA is the half adder, *mult2* is the 2-bit multiplier.196

- 5.13 Evolved 3-bit multiplier (E): Functional set {2, 7, 8, 9, 18, 22}; # logic gates = 42; # non-redundant primitive logic gates = 37; # building blocks = 18; HA is the half adder, mult2 is the two-bit multiplier. . . 197

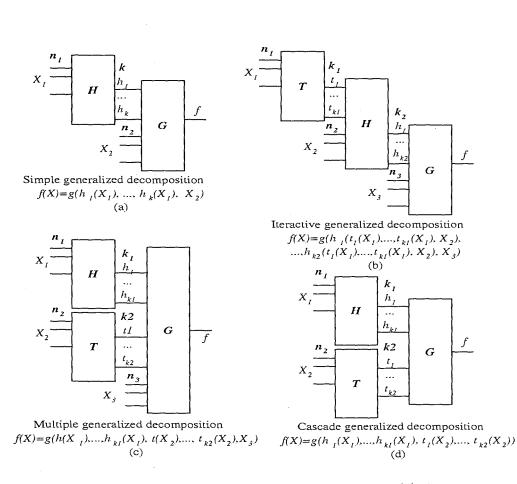

- 6.3 Circuit diagrams of functional decomposition. (a) Simple generalized decomposition; (b) Iteractive generalized decomposition; (c) Multiple generalized decomposition; (d) Cascade generalized decomposition. 214

xxiv

| 6.5  | Sub-circuits allocation in the complex circuit genotype (Sub-circuit con-                       |     |

|------|-------------------------------------------------------------------------------------------------|-----|

|      | nections include the logic gates that link sub-circuits with each other                         | 219 |

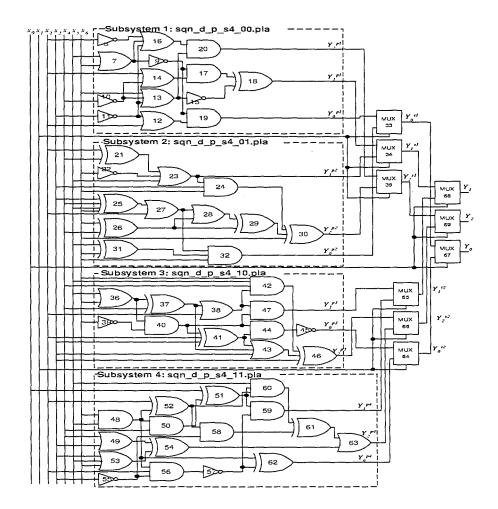

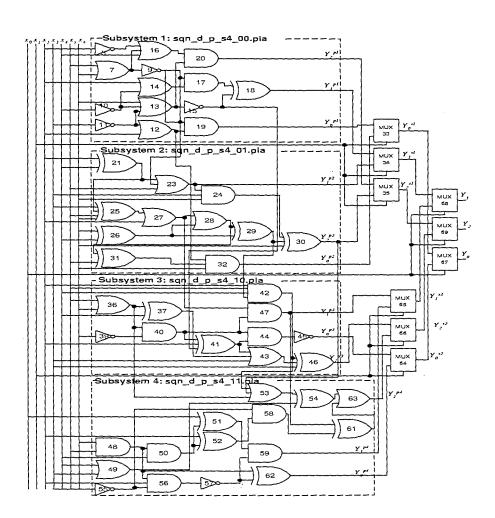

| 6.6  | sqn_d.pla: Designed circuit using Shannon's decomposition and function-                         |     |

|      | level EHW (Stage 2. Evolution towards an optimised system). The                                 |     |

|      | number of primitive logic gates: 93                                                             | 221 |

| 6.7  | sqn_d.pla: Circuit design using BIE with output decomposition and                               |     |

|      | function-level EHW (Stage 1. Evolution toward a modularised system).                            |     |

|      | The number of primitive logic gates: 50                                                         | 222 |

| 6.8  | sqn_d.pla: Circuit design using BIE with output decomposition and                               |     |

|      | function-level EHW (Stage 2. Evolution towards an optimised circuit).                           |     |

|      | The number of primitive active logic gates: 34                                                  | 224 |

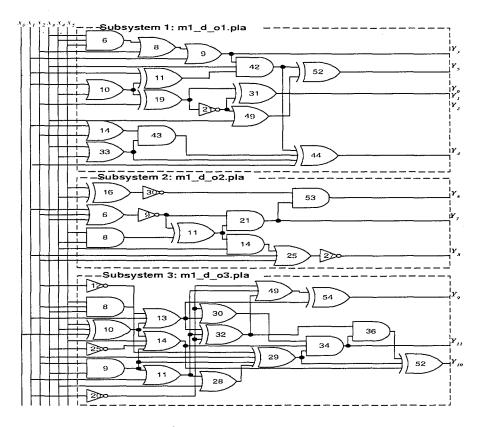

| 6.9  | m1_d.pla: Circuit design using BIE with output decomposition and                                |     |

|      | function-level EHW (Stage 1: Evolution towards a modularised sys-                               |     |

|      | tem). The number of primitive logic gates is 61                                                 | 225 |

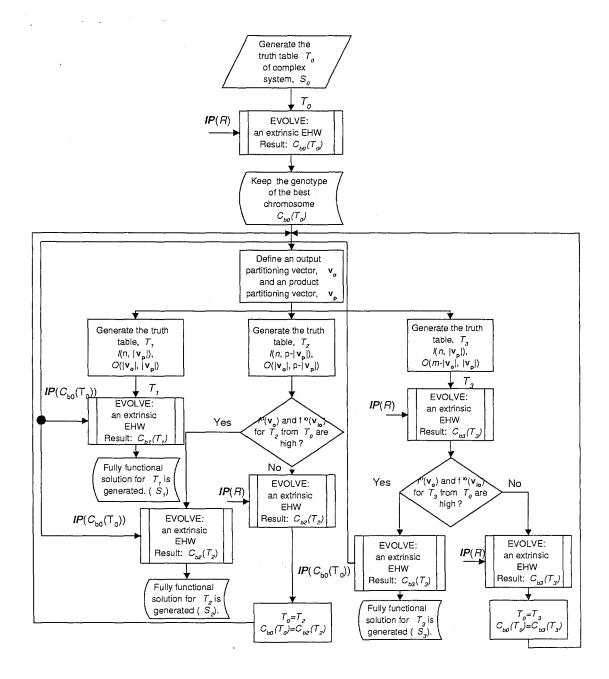

| 6.10 | The diagram of EHW-oriented decomposition. IP is the initial popula-                            |     |

|      | tion; $IP(R)$ denotes the randomly generated initial population; $T_i$ is the <i>i</i> -th      |     |

|      | truth table; $C_{bi}(T_i)$ is the best chromosome genotype evolved using an ex-                 |     |

|      | trinsic EHW for the function given by the truth table $T_i$ ; $\mathbf{IP}(C_{bi}(T_i))$ is the |     |

|      | initial population generated using the best chromosome genotype obtained                        |     |

|      | after the evolutionary process for the $i$ -th truth table                                      | 231 |

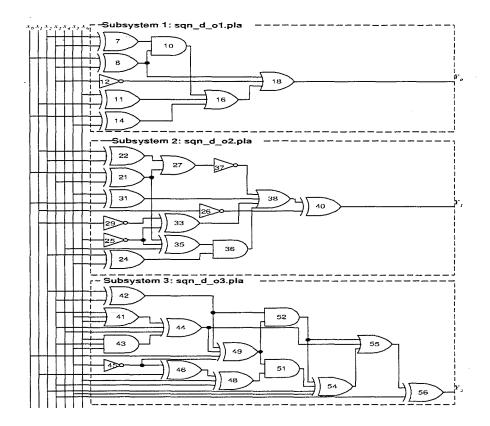

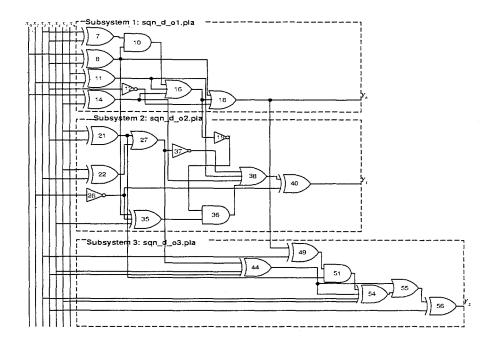

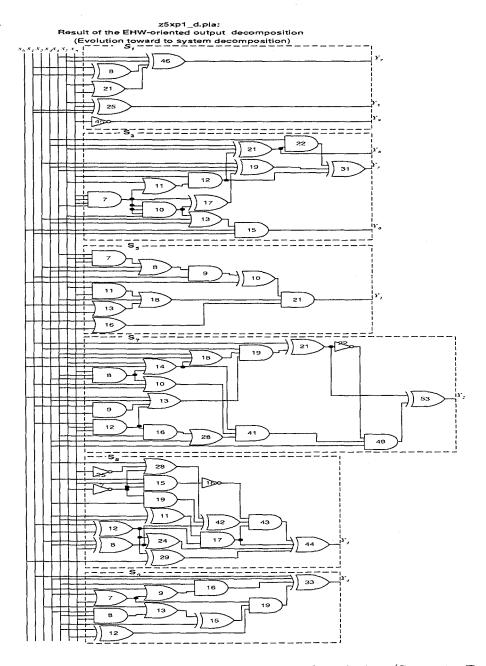

| 6.11 | z5xp1_d.pla: Bidirectional incremental evolution (Stage 1: Evolution                            |     |

|      | towards to a modularised system)                                                                | 236 |

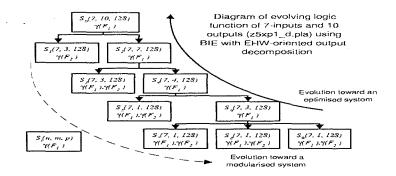

| 6.12 | z5xp1_d.pla: Diagram of performing a bidirectional incremental evo-                             |     |

|      | lution (Experiment C). The <i>i</i> -th system $S_i$ is evaluated according to the              |     |

|      | truth table of $n$ inputs, $m$ outputs and $p$ input-output combinations. This                  |     |

|      | evaluation process can be defined as $S_0(n, m, p)$ . Dynamic fitness function                  |     |

|      | [1] contains evaluation of: (1) circuit functionality, $F_1$ ; (2) the number of                |     |

|      | logic gates used in the circuit, $F_2$ . $\Upsilon(F_j)$ defines the evaluation process         |     |

|      | performed using criteria $F_i$                                                                  | 237 |

xxv

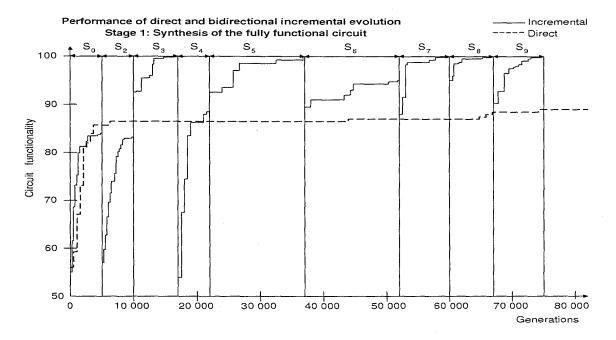

| 6.13 | z5xp1_d.pla: Performance of direct and bidirectional incremental evo-                              |     |

|------|----------------------------------------------------------------------------------------------------|-----|

|      | lution in the circuit design problem. The maximum fitness per generation                           |     |

|      | is plotted for each of the two approaches. The direct evolution (dotted line)                      |     |

|      | makes slight progress at the first and stalls after about 10 000 generations.                      |     |

|      | The plot is an average of 100 simulations. Incremental evolution, however,                         |     |

|      | proceeds through several task transitions (seen as abrupt drop-offs in the                         |     |

|      | plot), and eventually solves the goal-task. The incremental plot is a result                       |     |

|      | of one simulation.                                                                                 | 240 |

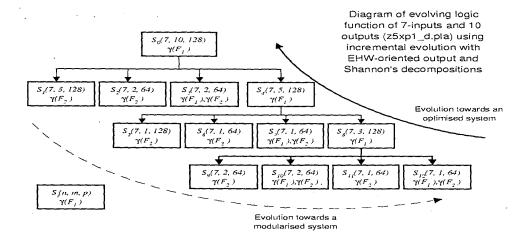

| 6.14 | z5xp1_d.pla: Diagram of performing bidirectional incremental evolu-                                |     |

|      | tion with output and Shannon's decompositions (Experiment D). $\$ .                                | 246 |

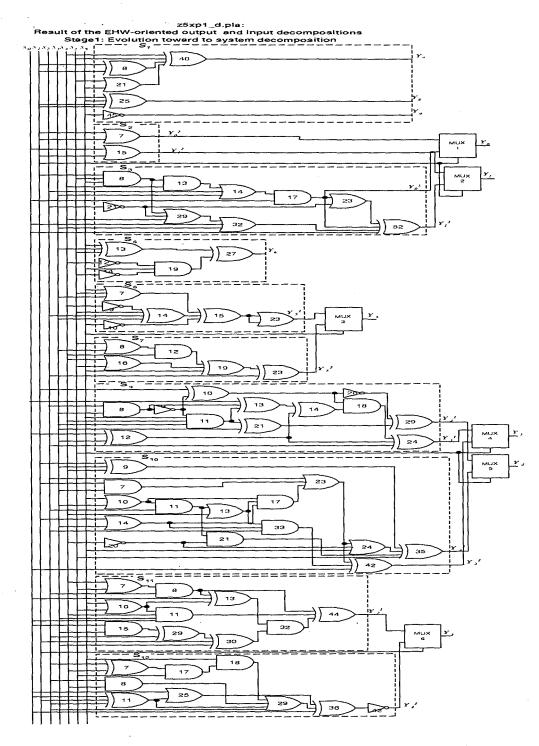

| 6.15 | z5xp1_d.pla: The EHW-oriented output and Shannon's decompositions                                  |     |

|      | (Stage 1: Evolution towards a modularised system) (Experiment D)                                   | 248 |

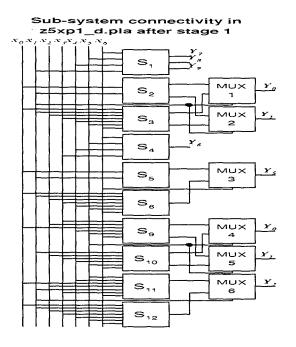

| 6.16 | Sub-system connectivity in z5xp1_d.pla: The EHW-oriented output                                    |     |

|      | and Shannon's decompositions (Stage 1: Evolution towards system                                    |     |

|      | decomposition). $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$            | 250 |

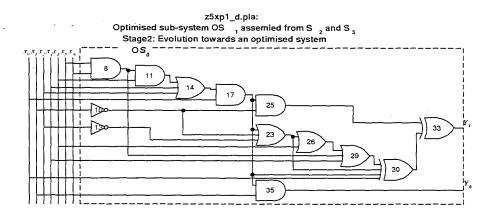

| 6.17 | z5xp1_d.pla: Optimised sub-system $OS_0 = \{S_2, S_3\}$ . The number of                            |     |

|      | primitive active logic gates is 18                                                                 | 251 |

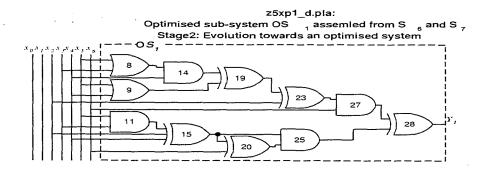

| 6.18 | z5xp1_d.pla: Optimised sub-system $OS_1 = \{S_6, S_7\}$ . The number of                            |     |

|      | primitive active logic gates is 12.                                                                | 252 |

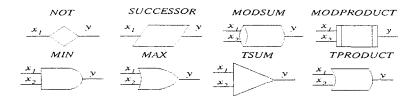

| 7.1  | Symbols of the two-input <i>r</i> -valued logic gates                                              | 261 |

| 7.2  | Building block level representation                                                                | 266 |

| 7.3  | Circuit level representation                                                                       | 267 |

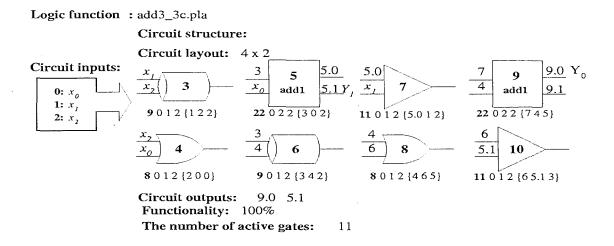

| 7.4  | An example of the phenotype and corresponding genotype of a chro-                                  |     |

|      | mosome with $4x^2$ circuit layout $\ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots \ldots$ | 270 |

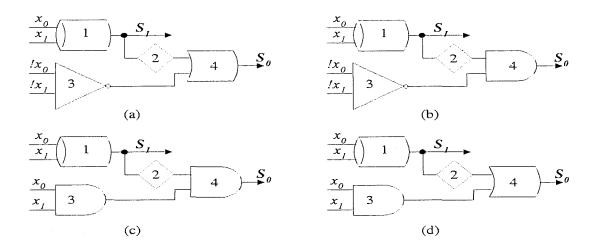

| 7.5  | The evolved for 3-valued half adder designs.                                                       | 276 |

| 7.6  | The evolved 3-valued full adders.                                                                  | 277 |

| 7.7  | The 3-valued 1-digit full adders evolved using the 3-valued half adder                             |     |

|      | and the one-digit multiplier                                                                       | 278 |

| 7.8  | The evolved 3-valued one-digit multiplier.                                                         | 279 |

|      |                                                                                                    |     |

xxvi

| 7.9  | The 3-valued 1.5-digit multipliers evolved using the 3-valued half adder               |      |

|------|----------------------------------------------------------------------------------------|------|

|      | and the one-digit multiplier.                                                          | 280  |

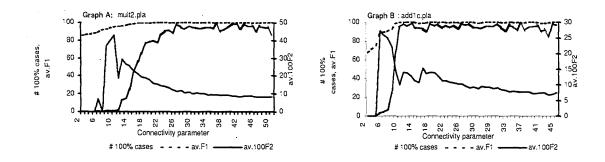

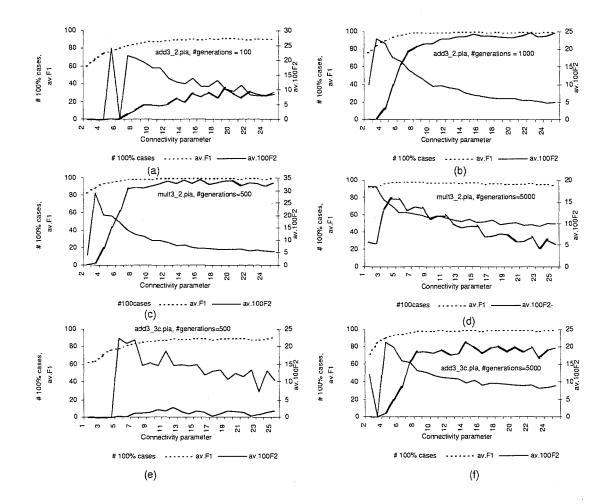

| 7.10 | Dependence of the algorithm performance on the connectivity param-                     |      |

|      | eter. These graphs shows that the algorithm performance depends on the                 |      |

|      | connectivity parameter. There is a range within which the algorithm per-               |      |

|      | forms very poorly. The curves are similar to ones, obtained for binary logic           |      |

|      | design problem (see Fig. 4.1). This confirms that the approach behaves                 |      |

|      | similar to both application tasks                                                      | 286  |

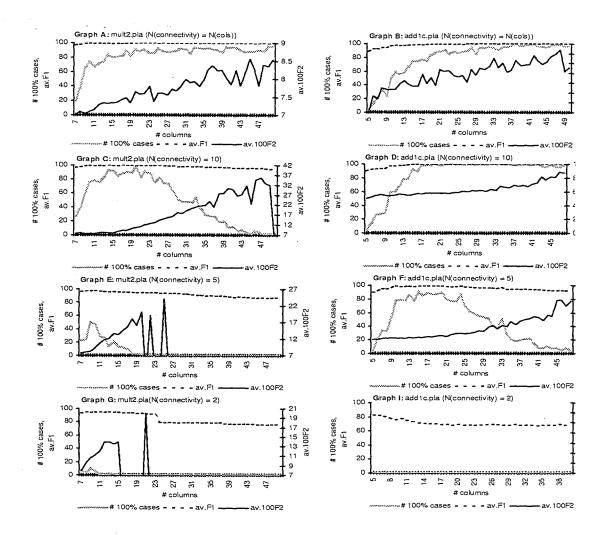

| 7.11 | Dependence of the algorithm performance on the number of columns.                      |      |

|      | The experiments depicted in these graphs have been performed with connec-              |      |

|      | tivity parameter $N_{connect} = N_{cols}$ , i.e. there is no connectivity restrictions |      |

|      | in the circuit. First, graphs show how with increasing the number of genera-           |      |

|      | tions the behaviour of algorithm changes. Thus, with increasing the number             |      |

|      | of generations the algorithm performance has been significantly improved.              |      |

|      | Comparing the obtained data with ones illustrated in Fig. $4.3$ for binary             |      |

|      | logic design problem, one can notice that the curves illustrate the same               |      |

|      | behaviour. This proves that the algorithm behaves similar for both problems            | .287 |

| 7.12 | Dependence of the algorithm performance on the number of rows.                         |      |

|      | Graphs illustrate that the algorithm performance does not depend on the                |      |

|      | number of rows in the rectangular array. Similar results have been obtained            |      |

|      | for binary combinational logic design problem (see Fig. 4.4).                          | 288  |

| A.1  | Overall view of a Xilinx FPGA (courtesy [10])                                          | 303  |

|      | Virtex Architecture (courtesy [11]).                                                   | 304  |

|      | CMOS dynamic gate.                                                                     | 306  |

|      | NOT logic gate, $F = \overline{A}$ : (a) Truth table, (b) Distinctive-shape symbol,    |      |

|      | (c) NMOS circuit, (d) PMOS circuit, (e) CMOS circuit, (f) CMOS                         |      |

|      | dynamic circuit.                                                                       | 308  |

xxvii

| A.5  | NOR logic gate, $F = \overline{A \vee B} = \overline{A + B}$ : (a) Truth table, (b) Distinctive-        |     |

|------|---------------------------------------------------------------------------------------------------------|-----|

|      | shape symbol, (c) NMOS circuit, (d) PMOS circuit, (e) CMOS circuit,                                     |     |

|      | (f) CMOS dynamic circuit                                                                                | 308 |

| A.6  | NAND logic gate, $F = \overline{A \wedge B} = \overline{A \cdot B}$ : (a) Truth table, (b) Distinctive- |     |

|      | shape symbol, (c) NMOS circuit, (d) PMOS circuit, (e) CMOS circuit,                                     |     |

|      | (f) CMOS dynamic circuit                                                                                | 309 |

| A.7  | AND logic gate, $F = A \wedge B = A \cdot B$ : (a) Truth table, (b) Distinctive-                        |     |

|      | shape symbol, (c) CMOS circuit.                                                                         | 309 |

| A.8  | OR logic gate, $F = A \lor B = A + B$ : (a) Truth table, (b) Distinctive-                               |     |

|      | shape symbol, (c) CMOS circuit.                                                                         | 310 |

| A.9  | EXOR logic gate, $F = A \oplus B$ : (a) Truth table, (b) Distinctive-shape                              |     |

|      | symbol.                                                                                                 | 310 |

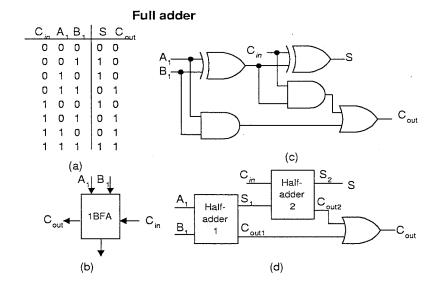

| A.10 | ) Half-adder: (a) Truth table; (b) Circuit.                                                             | 312 |

| A.11 | One-bit full adder (1BFA): (a) Truth table; (b) Distinctive-shape sym-                                  |     |

|      | bol; (c) Circuit; (d) Circuit with half-adders                                                          | 312 |

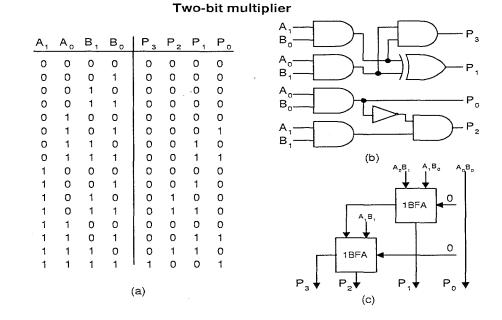

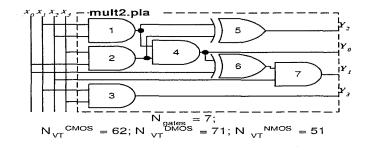

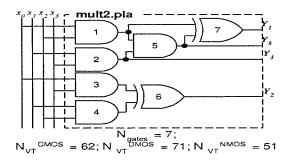

| A.12 | 2 Two-bit multiplier: (a) Truth table; (b) Conventional circuit; (c) Cir-                               |     |

|      | cuit with the one-bit full-adders (1BFA). In this work the two-bit multi-                               |     |

|      | plier is described, by input vector $X = \{x_0, x_1, x_2, x_3\}$ and the output vector                  |     |

|      | $Y = \{y_0, y_1, y_2, y_3\}, \text{ where } x_0 = A_1, x_1 = A_0, x_2 = B_1, x_3 = B_0, y_0 = P_3,$     |     |

|      | $y_1 = P_2, y_2 = P_1$ and $y_3 = P_0.$                                                                 | 313 |

| C.1  | Evolved two-bit multiplier design (A)                                                                   | 322 |

| C.2  | Evolved two-bit multiplier design (B) $\ldots$ $\ldots$ $\ldots$ $\ldots$                               | 323 |

| C.3  | Evolved two-bit multiplier design (C) $\ldots \ldots \ldots \ldots \ldots \ldots$                       | 323 |

|      |                                                                                                         |     |

•

#### xxviii

## List of Symbols

There follows the lists of symbols and abbreviations used in this thesis.

### Abbreviations

-

| BIE   | Bidirectional Incremental Evolution     |

|-------|-----------------------------------------|

| BGM . | Boundary Geometry Mutation              |

| CL    | Circuit Layout                          |

| CMOS  | Complementary metal oxide semiconductor |

| DMOS  | Dynamic CMOS                            |

| EA    | Evolutionary Algorithm                  |

| EHW   | Evolvable Hardware                      |

| ES    | Evolutionary Strategy                   |

| Eq.   | Equation                                |

| FA    | Full Adder                              |

| Fig.  | Figure                                  |

| FET   | Field-Effect Transistor                 |

| FPGA  | Field Programmable Gate Array           |

| HW    | Hardware                                |

| GA    | Genetic Algorithm                       |

xxix

| Global Geometry Mutation      |

|-------------------------------|

| Geometry Mutation             |

| Genetic Programming           |

| Half Adder                    |

| Local Geometry Mutation       |

| a 2-bit multiplier            |

| a 3-bit multiplier            |

| Multi-Valued Logic            |

| Programmable Logic Array      |

| Software                      |

| Variable-length chromosome ES |

| Variable-length chromosome GA |

|                               |

## Symbols

| y(X)                            | the logic function                                                                                                                                                                      |

|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| r                               | the radix of logic; $r = 2$ corresponds to the Boolean logic                                                                                                                            |

| n                               | the number of variables in the logic function                                                                                                                                           |

| m                               | the number of outputs in the logic function                                                                                                                                             |

| p                               | the number of input combinations in the logic function; $p = r^n$ corresponds to the completely specified logic function; $p < r^n$ defines that the function is incompletely specified |

| X                               | the set of input variables, $X = \{x_0, x_1,, x_{n-1}\}$                                                                                                                                |

| Y                               | the set of output variables, $Y = \{y_0, y_1,, y_{m-1}\}$                                                                                                                               |

| ${\cal F}$                      | the fitness function                                                                                                                                                                    |

| $\mathcal{F}_1 + \mathcal{F}_2$ | the dynamic fitness function                                                                                                                                                            |

| $F_1$ .                          | the percentage of correct output bits in evolved circuit                                                                                               |

|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|

| $F_2$                            | the number of active primitive logic gates in the circuit                                                                                              |

| $F_3$                            | the percentage of correct output combinations in evolved circuit                                                                                       |

| $F_4$                            | the cost of circuit in terms of the number of used transistors, resistors,                                                                             |

|                                  | capacitors, etc.                                                                                                                                       |

| $F_i^{bc}$                       | the $i$ -th fitness criteria of the best evolved chromosome                                                                                            |

| $\overline{F_i^{bc}}$            | the mean <i>i</i> -th fitness criteria of the best chromosome                                                                                          |

| $\overline{F_2(\mathcal{N}_f)}$  | the mean fitness function $F_2$ of fully functional designs evolved during                                                                             |

|                                  | R runs                                                                                                                                                 |

| FS                               | the functional set of logic gates                                                                                                                      |

| $ \mathcal{FS} $                 | the number of elements in the functional set of logic gates, $\mathbb{FS}$                                                                             |

| $\mathcal{N}$                    | the circuit or network                                                                                                                                 |

| $\mathcal{N}_{f}$                | the fully functional circuit                                                                                                                           |

| $cost(\mathcal{N})$              | the cost or size of the circuit $\mathcal{N}$                                                                                                          |

| $cost(\mathcal{N}^{max})$        | the maximum cost of the circuit $\mathcal N$                                                                                                           |

| $\mathcal{B}_z$                  | the building block ${\cal B}$ labeled $z$                                                                                                              |

| $cost(\mathcal{B}_z)$            | the cost or size of the the building block $\mathcal{B}_z$                                                                                             |

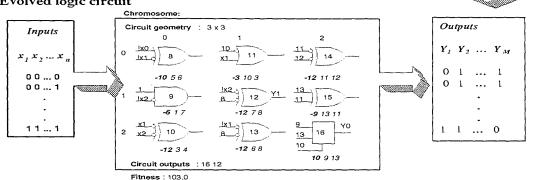

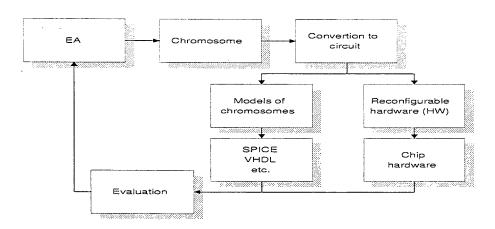

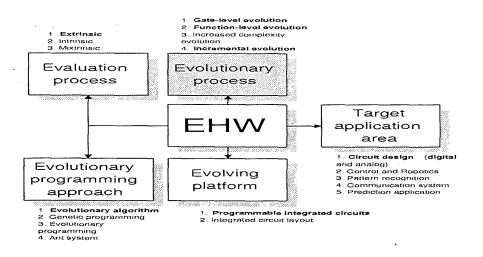

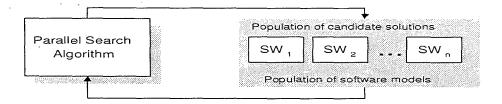

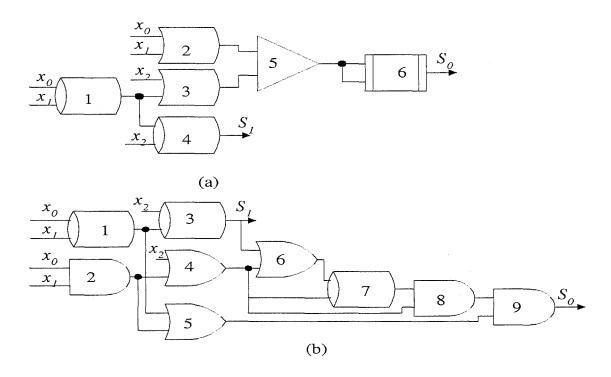

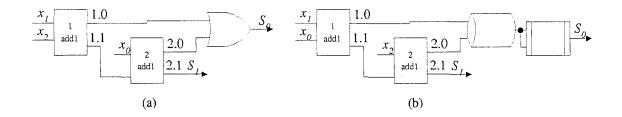

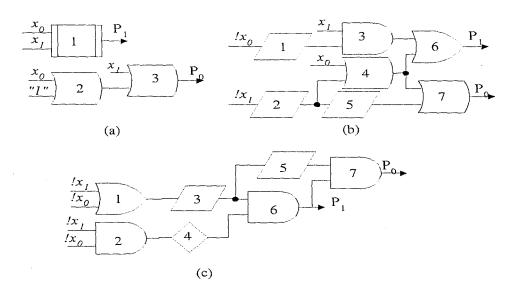

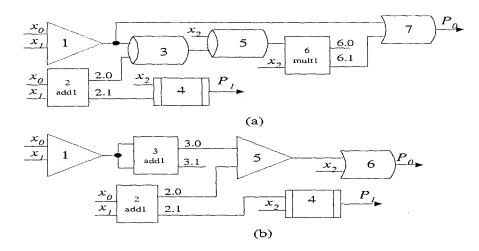

| $\mathcal{B}(c_{col}, c_{row})$  | the building block $\mathcal B$ located in column $c_{col}$ and row $c_{row}$                                                                          |